Chiplet结合先进封装已成趋势

在摩尔定律推进速度放慢与先进制程成本越来越昂贵的情况下,为了获得更高效能、更高整合度,且具有成本效益的芯片,越来越多半导体业者开始采用Chiplet架构来设计自己的芯片,再透过先进封装技术来实现整合。许多实际案例显示,结合Chiplet跟先进封装的IC元件,不仅在成本方面具有竞争力,而且可以提升元件效能,或实现更复杂的功能整合。但以Chiplet架构来设计元件,也会为设计团队带来挑战。

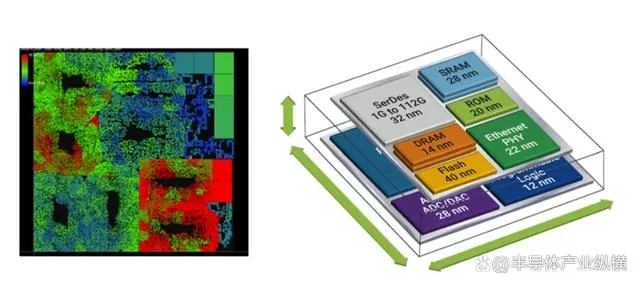

元件的功耗跟散热问题,一直是芯片设计者必须面对的主要挑战,而这些问题在采用Chiplet与先进封装后,会变得更复杂。因为一个封装体内将整合多枚晶粒(Die),且不同晶粒的功耗与发热状况可能会有很大的差异,在进行设计签核时,必须要用新的工具平台来加以应对。此外,热(Thermal)所带来的膨胀效应,也会让设计团队必须更谨慎地处理机械应力方面的问题。因为不同晶粒的发热状况不同,意味着不均匀的膨胀,产生更大的应力,对元件的可靠度产生负面影响。

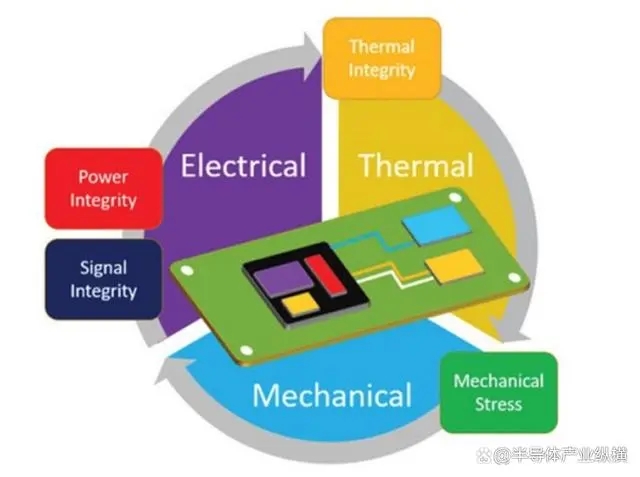

采用Chiplet架构,会让设计团队面对更复杂的电、讯号、热,以及应力问题。设计团队必须导入支援多重物理模拟的签核工具平台,才能准确地找出设计可能存在的问题并加以修正。本文将以Redhawk-SC Electrothermal(ET)为主,探讨在Chiplet时代,IC设计者所面临的挑战与解方。

老问题变得更加难缠

对IC设计者而言,不管是电源完整性(Power Integrity)、讯号完整性(Signal Integrity)、热,以及其所衍生的机械应力/翘曲,都是存在多年的挑战。但具有2.5D中介层或3D堆叠技术的现代多晶粒封装,会把这些问题变得更复杂。由Chiplet组装出复杂的整合系统,会让电源、讯号与热的问题更紧密地耦合起来。要准确预测这些系统整体行为的唯一方法是采用统一的分析环境,将多种工具中领先市场的引擎整合成同时多重物理量解决方案。

前面所提到的这些挑战,根源都来自于芯片上的电源,要对这些彼此耦合的问题进行分析,必须从电源分析着手。Ansys的Redhawk-SC一直是业界的黄金标准,尤其是在分析电压压降(IR Drop)跟电子迁移(Electron Migration)这些应用方面。但针对Chiplet跟先进封装所带来的挑战,设计团队需要更专用的工具,因此Ansys在Redhawk-SC的基础上,Ansys开发出Redhawk-SC Electrothermal(ET)这项延伸工具。

与典型的Redhawk-SC相比,Redhawk-SC ET可更仔细地解决多晶粒2.5D/3D IC结构的电气和热多重物理量互动。它使用来自Ansys RedHawk-SC的引擎,包括热与机械工具来解出异质系统的功率和应力运算式。因此,Ansys RedHawk-SC ET可以解算精准的电热、机械应力和位移运算式。同时,也使用了RedHawk-SC的弹性运算基础架构,可以同时分析多达十亿个执行个体(Instance)。

Ansys RedHawk-SC Electrothermal为一个基于业界标准的多物理场的芯片封装系统模拟平台。

当设计人员在执行热分析时,Redhawk-SC ET还能自动启动AEDT/Icepak这类系统层级的分析工具,以便从中取得边界条件。这项特性对于解决Chiplet这种本质上十分接近系统等级的设计专案而言,是相当关键的。

在讯号一致性方面,先进封装内部不仅互联的数量远胜过传统封装,互联的速度也更快,如何确保在内部互联中传递的讯号正确无误,也是设计团队面临的主要挑战。RedHawk-SC ET透过支援在多晶粒封装的整个3D堆叠中,撷取讯号和电源互连的RC寄生元件,协助设计人员对先进封装设计的讯号完整性进行评估。

早期原型回馈/阶层式建模提升设计生产力

除了专为Chiplet/先进封装所设计的全面性模拟分析功能外,Redhawk-SC ET还有一个特殊功能,就是让早期原型设计的工作变得更有效率。该工具可根据每个区块的早期电源估计值,提供关于封装的热和电源完整性特性的早期原型回馈。所有结果都会显示在互动式多晶粒检视器中以便进行分析。设计人员进行原型设计时,能很快地评估设计完成后的大致结果,减少设计团队走冤枉路的风险。

在设计流程中之所以会有签核程序的存在,就是为了在产品实际投产之前,早一步找出设计中可能存在的问题,进而加以修正,减少设计团队投入时间跟资金后,得到有问题的产品机率。因此,一个理想的签核工具平台,必须要具备跟前段设计无缝衔接,彼此互动的能力,方能达到缩短设计时间,提高设计人员生产力的目标。在Redhawk-SC ET里面,Ansys特别规画早期原型回馈这项功能,让设计团队在原型开发的早期阶段,就能大致评估最终设计的结果。

为了让设计团队能应对Chiplet/先进封装这种极为复杂的设计专案,Redhawk-SC ET采用了广泛的阶层式建模格式,让复杂的专案能有更清晰明了的结构。此外,整个3D组合件必须放置在完整的最上层系统视图的分析中。RedHawk-SC ET透过拥有大量降阶模型的材料库来加速这项作业,撷取电源、热、讯号完整性及ESD行为,以利简单进行精简交换与阶层式分析。

Ansys RedHawk-SC Electrothermal为一个基于业界标准的多物理场的芯片封装系统模拟平台。

签核/设计实为一体两面无缝衔接至为重要

在设计与设计签核之间实现无缝衔接,甚至在某种程度上做到互相融合,是EDA工具未来很重要的发展趋势。在设计专案日益复杂,开发时间却没有增加的今天,IC设计团队都面临巨大的产品上市时程压力。

为了缓解时间压力,在个别工具层面,IC设计者希望工具能有更强大的平行处理能力,例如支援更多CPU,来缩短工具的执行时间(Runtime)。在工具执行效率方面,Redhawk-SC ET建立在Seascape巨量资料分析平台上,这是专为执行具有1,000个CPU核心的云端所设计,具备近线性的可扩充性和极高容量,且每个核心占用的记忆体很低。开发团队可以用相对低的云端/硬体基础建设成本来完成分析作业。

流程的优化也很重要,要做到这点,工具之间的水平与垂直融合,是最基本的要求。多重物理模拟就是水平整合的代表,藉由将电源、讯号、应力分析引擎融合为一,Redhawk-SC ET将Chiplet/先进封装设计所需要执行的设计签核流程变得更单纯、也更有效率。早期原型反馈则是希望能在垂直整合方面走得更远,让设计团队从一开始就朝正确的方向迈进,提高团队的生产力。