先进封装之困

多芯片组装为提升性能和降低功耗提供了重要机会,但这些复杂的封装也带来了许多新的挑战,包括芯片到RDL错位、不断变化的翘曲轮廓和CTE不匹配。

异构集成——一个涵盖众多不同应用和封装要求的总称——具有将采用多种不同工艺的组件整合到单一封装中的潜力。与将相同组件集成在单片硅片上相比,这种集成方式可能更具成本效益,并带来更高的良率。

与传统电路板上的独立元件相比,将器件集成到单个封装中也能提高性能,并减少电路的整体占用空间。但将这些不同的元件集成到单个基板上是一项重大挑战。

以移动设备为例。这些设备通常包含多个传感器和收发器,以及存储器和逻辑组件。模拟和功率组件通常需要CMOS器件制造中没有的独特工艺步骤,以及更厚的金属和介电层。

这些问题的研究大多处于半导体设计的前沿。但如果能够解决集成挑战,相对较小的市场也将受益匪浅。弗劳恩霍夫IZM公司组装和封装部门主管兼集团经理Tanja Braun在材料研究学会(MRS)最近举办的2025年MRS春季会议期间举办的“微电子封装和异质集成材料机遇”研讨会上发表演讲时表示,实现这一目标的方法之一是开发能够跨不同应用领域的解决方案。

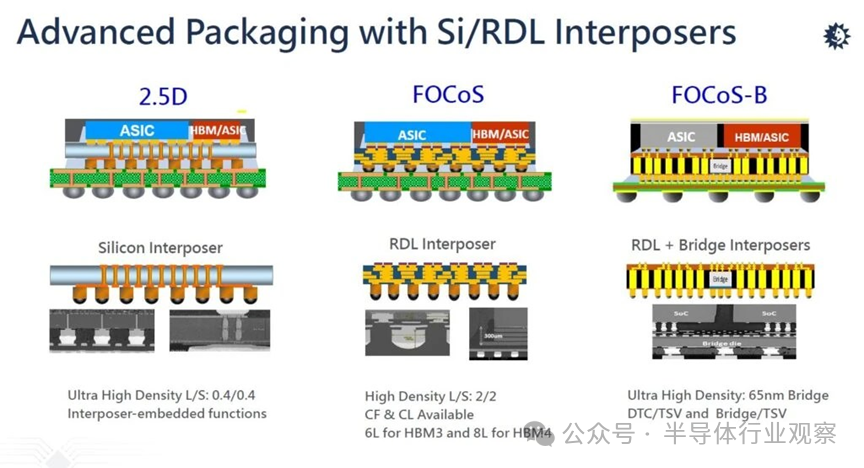

中介层将组件连接在一起。

如今,大多数异构组件都使用某种形式的中介层,将电路组件彼此连接并与外界连接。单个器件可以放置在中介层上,并通过扇出布线和集成电容器或其他无源元件进行连接。光学元件可能依赖于中介层中嵌入的波导。多个处理单元可以通过带有嵌入式布线的桥接元件连接,例如英特尔的嵌入式多芯片互连桥接(EMIB)。

在所有情况下,所需的互连和功率密度决定了中介层材料的选择。但它们都面临着同样的根本挑战——管理硅器件和铜基系统级布线之间的热膨胀系数(CTE)差异。弗劳恩霍夫的Braun指出,当她的团队用铜柱填充有机电介质中的过孔时,CTE不匹配会导致收缩,从而引起铜-电介质界面出现裂纹。

对于功率器件而言,热膨胀系数(CTE)管理尤其困难,因为它们在运行过程中可能会产生大量热量。功率器件还需要可靠的隔离,以防止电弧放电并减少寄生损耗。玻璃满足隔离和热稳定性要求,但需要特殊处理。

宾夕法尼亚州立大学电气与计算机科学学院和材料研究所副教授李宁表示,光互连技术对于数据中心的中长连接至关重要,但也带来了独特的挑战。他指出,制造商希望将波导和其他无源光学元件集成到互连封装中,但这样做需要仔细控制基板中的折射率和折射率对比度。

尽管功率和光学器件带来了特殊的挑战,但即使是通用逻辑元件的中介层也需要与设计的其他部分共同优化。例如,扇出型面板级封装通常被认为是扇出型晶圆级封装的更高效的后继方案。面板可以并行处理更多器件,而且由于是矩形,在平铺矩形器件时浪费的空间更少。然而,Braun表示,它们的尺寸使其处于一个灰色地带。能够满足逻辑重分布层微米级尺寸要求的工艺和检测设备大多针对晶圆尺寸的基板进行了优化。即使有能够处理大型基板的设备,检测如此小尺寸的基板本身也非常缓慢。

将芯片固定在其放置位置

控制翘曲和芯片移位对于面板级封装尤其具有挑战性。芯片优先、面朝下的扇出工艺将单个芯片面朝下放置在载体基板上的转移胶带上。玻璃载体通常用于方便紫外线脱键合。将芯片封装在模塑料中后,释放转移胶带会将面板与载体基板分离,露出键合焊盘。将这些焊盘与中介层的重分布层布线对齐后,进行混合键合。

这个过程描述起来容易,实现起来难。转移胶带和模塑料(通常都基于聚合物)彼此之间以及与硅芯片和载体基板之间的热膨胀系数(CTE)都不同。转移胶带通常在成型过程中会膨胀,而模塑料在冷却和固化时会收缩。互补的应力会使面板变形,并可能将单个芯片从其原始位置拉出,从而与重新分布层失去对齐。

Braun指出,翘曲会在整个组装过程中不断演变。包含散热器、加强筋和模塑料在内的完整面板组件的翘曲程度可能比单独的封装芯片要小。因此,工艺优化应该评估整体结果,而不是某个特定的工艺步骤。

相比之下,一旦封装材料硬化,芯片偏移往往会“冻结”在原地。虽然已知的系统性偏移可以在RDL设计中得到适应,但热异常、模塑料的不均匀性以及类似因素可能会导致随机偏移。在这种封装中,芯片和RDL布线之间的错位尤其难以检测,因为连接两者的混合铜-铜键隐藏在两层之间。

自上而下的目视检查可以轻松检测到变形的焊球和断裂的引线键合,但无法检测到界面污染或错位的混合键合。对单个芯片和整个封装的测试仍然具有挑战性。

解决这些问题的不同方法正在涌现。英特尔高级首席工程师段刚和他的同事指出,该公司的EMIB封装尝试通过设计预制井来解决芯片移位错误,以便将芯片放置到硅“桥”元件中。

Braun团队提出的另一种方案依赖于无掩模光刻技术。在测量芯片的最终位置后,晶圆厂会相应地修改RDL焊盘的位置,并根据更新后的位置制造定制的中介层。该解决方案能否满足大规模生产的成本和产量要求尚不清楚。从技术上讲,RDL制造比PCB制造更接近CMOS互连工艺,但其面板面积比以晶圆为中心的设计工具通常设想的要大得多。

对于功率器件,研讨会参与者、马里兰大学机械工程教授F.Patrick McCluskey指出,封装是关键的差异化因素。他指出,这些器件本身相对简单,但需要低损耗、低噪声且热特性优异的封装。

然而,弗劳恩霍夫IZM的研究员蒂娜·托马斯及其同事表示,热场和电场的退化可能导致环氧基模具化合物变脆,有可能导致电介质击穿并允许湿气侵入。

除此之外,嵌入式无源元件会使整体封装更厚。因此,制造商需要考虑塑封料的流变特性及其均匀填充整个腔体的能力。硅凝胶是一种替代方案,它具有热稳定性和化学稳定性,并且是良好的绝缘体,但防水性不是特别好。

马里兰大学的研究人员展示了一种双层封装,它结合了防潮但坚硬的聚氨酯层和机械柔顺的硅胶层。

结论

异构封装模糊了“片上”和“片外”环境之间的界限。这也是为什么所有参与MRS研讨会的参与者都强调封装设计和组件器件需要协同优化的原因之一。每个器件的噪声和热特性及要求都会影响其他所有器件。像UCIe这样的标准化接口是一个良好的开端,但它们不能替代对拟议设计进行彻底的仿真。

参考链接

https://semiengineering.com/advanced-packaging-depends-on-materials-and-co-design/